# Design Guideline for Microfluidic Side Connect

Editors: Wilfred Buesink (Micronit) and Henne van Heeren (enablingMNT)

With contributions / suggestions and support from persons from the following organizations:

APIX, Axxicon, Blacktrace, CEA-Leti, enablingMNT, Fluigent, Microfluidic ChipShop, Microfluidic Consortium, Micronit, Philips, PhoeniX, TNO.

Comments, suggestions, and questions regarding this document can be addressed to:

Henne van Heeren enablingMNT –Netherlandshenne@enablingMNT.com 0031786300748

This work was supported by the MFManufacturing project, co-funded by grants from the UK, France and the Netherlands and the ENIAC / ECSEL Joint Undertaking.

Version 1.0 June 2017 DOI: 10.13140/RG.2.2.10982.83528

# Contents

| Cor      | ntents | S                                                                                                                           | 2 |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------|---|

| 1.       | Def    | finitions and interpretations                                                                                               | 3 |

| 3.       | Intr   | roduction                                                                                                                   | 4 |

| 3        | Def    | finition of reference axes                                                                                                  | 5 |

| 4        | Dim    | nensions                                                                                                                    | 7 |

| Z        | .1     | Side connect width and exclusion zone                                                                                       | 7 |

| Z        | .2     | Port pitch and size                                                                                                         | 7 |

| Z        | .3     | Layer thickness                                                                                                             | 8 |

| 5        | Арр    | olication classes                                                                                                           | 9 |

| 6        | Tub    | be compatibility                                                                                                            | 9 |

| 8        | Oth    | ner side connect considerations1                                                                                            | 0 |

| 9<br>chi |        | nmary table of all interconnect guideline dimensions and tolerances regarding port pitches,<br>knesses and port dimensions1 | 0 |

# 1. Definitions and interpretations

The terms stated here have the meaning as described below unless the context otherwise requires and explained at those places.

| Building block (BB)                | Component that fits with others to form a whole system. In        |  |  |  |  |

|------------------------------------|-------------------------------------------------------------------|--|--|--|--|

|                                    | the context of microfluidics, it means a microfluidic             |  |  |  |  |

|                                    | component that performs a certain function or set of              |  |  |  |  |

|                                    | functions. The building block is a single unit or product that    |  |  |  |  |

|                                    | can be assembled onto a fluidic circuit board (FCB) to create     |  |  |  |  |

|                                    | a functional system. Often the building block can be used         |  |  |  |  |

|                                    | independently. When the main function is a microfluidic           |  |  |  |  |

|                                    | operation a building block can also be referred to as             |  |  |  |  |

|                                    | microfluidic building block (MFBB)                                |  |  |  |  |

| Dead-volume                        | The portion of the internal volume of a system that is not        |  |  |  |  |

|                                    | part of a continuous flow-path. In this context dead signifies    |  |  |  |  |

|                                    | unmoving, stagnant, or un-swept.                                  |  |  |  |  |

| Edge connection                    | Connection to the edge of a surface                               |  |  |  |  |

| Edge exclusion                     | Area on the edge of the top or bottom surface that should         |  |  |  |  |

|                                    | be excluded from certain features or is reserved for certain      |  |  |  |  |

|                                    | features or functions.                                            |  |  |  |  |

| Fluidic circuit board (FCB)        | A fluidic device with microfluidic and or electrical routing      |  |  |  |  |

|                                    | and optionally some functionality able to have building           |  |  |  |  |

|                                    | blocks (BB) connected to it to form a microfluidic                |  |  |  |  |

|                                    | (sub)system.                                                      |  |  |  |  |

| Gasket                             | Mechanical (typically Elastomer) seal compressed between          |  |  |  |  |

|                                    | two components to prevent fluid leakage. May or may not           |  |  |  |  |

| Microfluidic building block (MFBB) | grip and seal onto a tube.<br>See building block                  |  |  |  |  |

| Multi-connector                    | Connector that houses a set of connections.                       |  |  |  |  |

|                                    |                                                                   |  |  |  |  |

| Multi-seal                         | Seal or gasket that enables a leak-free interface to an array     |  |  |  |  |

| Dout witch                         | of ports.                                                         |  |  |  |  |

| Port pitch                         | The distance between the centers of two adjacent ports.           |  |  |  |  |

| Reference point                    | The zero point in a 2 or 3-dimensional system. Distance           |  |  |  |  |

|                                    | values in relation to this point give an absolute value in x-, y- |  |  |  |  |

| Cool                               | or z-direction.                                                   |  |  |  |  |

| Seal                               | A seal is normally a sub-system of a connector comprising a       |  |  |  |  |

|                                    | component or components arranged at the end of a fluid            |  |  |  |  |

|                                    | path and when typically used with a connector will retain         |  |  |  |  |

| Cido connect width                 | fluid within a microfluidics system.                              |  |  |  |  |

| Side connect width                 | The length of the side of the chip where the side connector       |  |  |  |  |

| Cide composition                   | is to be placed.                                                  |  |  |  |  |

| Side connection                    | Connection to the side surface of a device perpendicular to       |  |  |  |  |

| Tour commention                    | the top surface.                                                  |  |  |  |  |

| Top connection                     | Connection to the top or bottom surface of a device on the        |  |  |  |  |

|                                    | x-y-plane.                                                        |  |  |  |  |

# 2. Introduction

The goal of this document is to provide guidelines for microfluidic devices having fluidic access point on the side of the device. In general, the MFM standards for top-down connectors and devices apply to the side connect as well. Some additional definitions and descriptions are needed for a proper guideline.

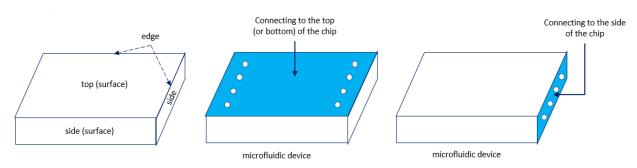

Figure 1: Schematics showing definitions of top, side and edge (left); top connection (middle) and side connection (right).

Making microfluidic connections to the side of a chip is a practical way for interfacing microfluidic devices, especially where low dead-volume, small sample volumes, shear rate, small device footprint and/or maximized optical access are critical.

Based on the available solutions and MFM standard guidelines summarized in the earlier MFM whitepapers the following topics are here proposed for standard guidelines:

- a) Side connect definitions.

- b) Side width and exclusion zone.

- c) Port pitch and size.

- d) Layer thickness.

- e) Use of classifications.

- f) Tube compatibility.

# **3 Definition of reference axes**

The objective of this part of the design guide is to provide a coherent system of reference axes used to describe positions on the chips. The convention is based on the chip manufacturing view point, not on the user who might take another view.

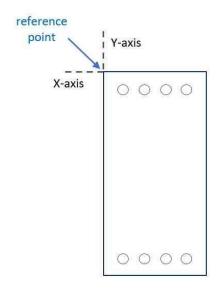

The naming of the chip defines the position of the XY axes. For instance, a 15\*30 mm chip has the X axes along the 15 mm side. The chip is then positioned with the X axis pointing from left to right. The Y axis is on the left of the viewer. The reference point is then on the top left of the chip (see next Figure).

Figure 2: 15\*30 mm<sup>2</sup> chip with axes and reference point.

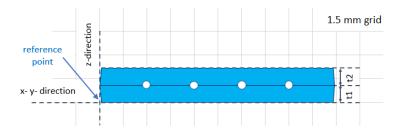

For a definition of side connectors, another set of definitions is needed; in the first place the Z-axis. Placing the chip horizontally which the reference point on the left, the Z axis is also on the left. (The reference is point determined by the outer edges of the chip.) The bottom layer is positioned on the x-y plane; the z-position is zero here.

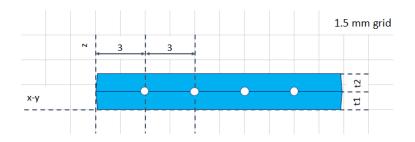

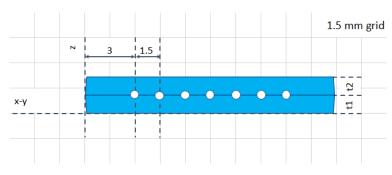

The thickness of the bottom layer is 't1', the top layer 't2'. Analog the earlier defined top connector ports<sup>1</sup> the port locations are on a 1.5 mm grid defined by the X and Z axes (see next figure).

Figure 3: Definitions of Z axis, top and bottom layer thickness, 1.5 mm grid.

<sup>&</sup>lt;sup>1</sup> See whitepaper: Design Guideline for Microfluidic Device and Component Interfaces Part 1 (MFM)

### **4 Dimensions**

### 4.1 Side connect width and exclusion zone

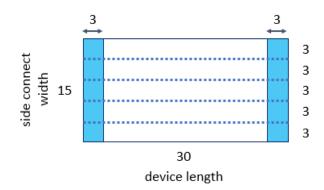

The recommend interfacing is designed for a 15 mm wide chip, but connectors for 30 mm width chips are also foreseen. The length of the chips is not specified in this standard, but it is recommended to follow the earlier guideline<sup>2</sup>. To ensure a leak tight and mechanically strong connector, on both edges of the chip a stroke of 3 mm width should be reserved for the support and clamping of the device. On these strokes, no optical structures or protruding structures are allowed (see next figure).

#### Figure 4: Exclusion zones for side connector for a 15\*30 mm<sup>2</sup> chip.

Note 1: If another side connect width is needed, use a width based on the 1.5 mm grid (preferred 3 mm grid).

### 4.2 Port pitch and size

The preferred port pitch is 3 mm, also starting with the first port at 3 mm from the outer edge (see figure 5).

#### Figure 5: port position based on a 3 mm pitch

For multi-port connectors and direct coupling (e.g. gluing) a 1.5 mm pitch can be used assuming the used connector and tubing are also compatible. For reliability reasons, it is not advised to use the first grid point, but keep a minimal distance of 3 mm to the side of the chip (see figure 6)

<sup>&</sup>lt;sup>2</sup> See whitepaper: Design Guideline for Microfluidic Device and Component Interfaces Part 1 (MFM)

Figure 6: port position based on a 3 mm pitch

The port size is not defined, as the process to make the channels on the microfluidic chip defines it, neither is the position of the center point in z-direction. Typically, the whole opening should be located within a circle with a diameter of 0.5 mm with regards to the center on the grid point. When working with thicknesses below 0.7 mm and or with small tubes and seals this size should be smaller and compatible with the components used.

*Note:* check the connector availability and customer specific options of the suppliers before fixing the port design (pitch and size).

### 4.3 Layer thickness

The following aspects should be considered when choosing the thicknesses of the layers:

- For a planar connection, often a symmetric design is preferred where 't1' = 't2'.

- The layer thickness 't1' is most often the supported thickness by the interface and therefore critical for the connector compatibility.

- The required interface holder is linked to 't1' and the device length. If needed the interface body can easily be customized to your device size.

Although there are many thicknesses of chip available, the following chip thickness combinations are advised:

|                   | Top layer 't2' |     |     |     |     |     |     |     |

|-------------------|----------------|-----|-----|-----|-----|-----|-----|-----|

|                   |                | 0.4 | 0.5 | 0.7 | 0.9 | 1.0 | 1.1 | 2.0 |

|                   | 0.2            |     |     | 0.9 |     |     | 1.3 |     |

| Bot               | 0.4            | 0.8 |     | 1.1 |     |     |     |     |

| Bottom layer 't1' | 0.5            |     | 1.0 |     |     |     |     |     |

| n lay             | 0.7            | 1.1 |     | 1.4 |     |     | 1.8 |     |

| /er               | 0.9            |     |     |     | 1.8 |     |     |     |

| Ę                 | 1.0            |     |     |     |     | 2.0 |     |     |

|                   | 1.1            |     |     | 1.8 |     |     | 2.2 |     |

|                   | 2.0            |     |     |     |     |     |     | 4.0 |

### Table 1: Preferred thicknesses of bottom- and top layer.

Comment: Always check the feasibility of your design and application compatibility of a device with a 't1' layer thickness thinner than 0.4 mm. The advised minimum thickness for 't1' and 't2' is 0.4 mm but also depending on the type of connector available.

# 5 Application classes

The side connect devices and connectors are typically compatible with most application classes<sup>3</sup> shown in the table below. Please check the compatibility of both the device and the planned connector.

| Table 2. | initial classification sche | The for finctonuluic devices, F | i denotes pressure and tempe |  |  |

|----------|-----------------------------|---------------------------------|------------------------------|--|--|

| Class    | Maximum                     | Maximum                         | Minimum                      |  |  |

| Туре     | Pressure                    | Temperature                     | Temperature                  |  |  |

|          | (bar)                       | (°C)                            | (°C)                         |  |  |

| PT 2/50  | 2                           | 50                              | 4                            |  |  |

| PT 2/75  | 2                           | 75                              | 4                            |  |  |

| PT 2/100 | 2                           | 100                             | 4                            |  |  |

| PT 7/50  | 7                           | 50                              | 4                            |  |  |

| PT 7/100 | 7                           | 100                             | 4                            |  |  |

| PT 30/50 | 30                          | 50                              | 4                            |  |  |

Table 2: Initial classification scheme for microfluidic devices; PT denotes pressure and temperature, respectively.

Additional comments:

- Depending on the connector the sealing onto the device is via individual seals per connection or via a multi-connector seal, sealing all connections at once.

- With the goal of realizing interoperability the preferred interfacing method are reusable connectors. For reliability and to prevent contamination, it might be advisable to use single use seals.

- For pitches of 1.5 mm or smaller (in future standards) a multi-connector is advised for easy handling.

### 6 Tube compatibility

Typical tube outer dimensions (OD) for side connect devices in microfluidic applications are:

- 1/16" (≈1.6 mm)

- 1/32" (≈0.8 mm)

Do keep in mind that a specific connector usually only supports a single specific tube size.

Smaller sized tubes and capillaries can be beneficial for 1.5 mm pitch side connect applications; preferred tubes outer diameters are:

- 0.5 mm (usually between 0.44-0.53 mm)

- 0.36 mm (usually between 0.35-0.38 mm)

*Note:* Do keep in mind that making a leak free connection to the side of the chip is not an easy task. Depending on the technology used (glass, injection molding etc.) care is needed to create a smooth contact surface for the seal.

<sup>&</sup>lt;sup>3</sup> The defined classes are based on ISO IWA 23: Interoperability of microfluidic devices: Guidelines for pitch spacing dimensions and initial device classification

### 7 Other side connect considerations

Some considerations for use of side connectors other than described in these guidelines:

- For connections with a Fluidic Circuit Board (FCB) typically a top-down connection is advised. Side connect devices can be used that link the ports on the side of the chip to the port on the surface of the FCB.

- Dedicated connectors to interface two chips with side connection ports are foreseen; however, if possible it is preferred to combine the building block designs into a single chip.

# 8 Summary table of all interconnect guideline dimensions and tolerances regarding port pitches, chip thicknesses and port dimensions

The relevant guidelines for side connectors are summarized in the table below:

| Parameters                                                                                              | Nominal<br>value | Minimal<br>value | Maximal<br>value | Tolerance* |

|---------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|------------|

| Distance of the first hole from the Z axis                                                              | 3                |                  |                  | +/- 0.15   |

| Distance between holes or port pitch (+/-<br>radius from nominal distance in relation<br>to first hole) | n*1.5            | 1.5              |                  | +/- 0.10   |

| Total Chip Thickness                                                                                    | 0.8              | 0.7              | 0.9              | +/- 0.1    |

| Total Chip Thickness                                                                                    | 1                | 0.9              | 1.1              | +/- 0.1    |

| Total Chip Thickness                                                                                    | 1.1              | 1.0              | 1.2              | +/- 0.1    |

| Total Chip Thickness                                                                                    | 1.4              | 1.3              | 1.5              | +/- 0.1    |

| Total Chip Thickness                                                                                    | 1.8              | 1.65             | 1.95             | +/- 0.15   |

| Total Chip Thickness                                                                                    | 2                | 1.80             | 2.20             | +/- 0.20   |

| Total Chip Thickness                                                                                    | 4                | 3.60             | 4.40             | +/- 0.20   |

| Tight tolerance of outer chip dimension (desired)                                                       | n * 15           | 15               | 30               | +/- 0.05   |

| Lower tolerance of outer chip dimension (when tight tolerance not achievable)                           |                  |                  |                  | +/- 0.15   |

Table 3: chip dimensions and tolerances (all values in mm)

\* Please note that not all dimensions fit in these tolerances and depending on the design, material and interface solution selected the required tolerance can be smaller or larger. As mentioned in the guideline in many cases the tolerance on the bottom layer (t1) is more important for the interfacing than the total tolerance (allowing for instance PSA tape bonding that add to the total thickness)