# Design Guideline for Microfluidic Device and Component Interfaces (part 1)

#### **Editors:**

Henne van Heeren (enablingMNT), Tim Atkins (Blacktrace/Dolomite), Nicolas Verplanck and Christine Peponnet (CEA-LETI), Peter Hewkin (CfBI), Marko Blom and Wilfred Buesink (Micronit), Jan-Eite Bullema (TNO), Stefan Dekker (University of Twente).

With contributions / suggestions and support from persons from the following organisations:

APIX, Axxicon, Bronkhorst, CEA-Leti, CfBI, CMC Microsystems, Corsolution, Cytocentrics, Diagnostics Biosensors, DIBA, Dolomite, enablingMNT, EV Group, EVEON, Fluigent, Fraunhofer IOF, IHP, IMTag, IMTEK, Invenios, IPHT, IVAM, LioniX, Memsmart, Microfluidic ChipShop, Microfluidic Consortium, Micronit, MinacNed, NIST, Philips, PhoeniX, Qmicro, SCHOTT Technical Glass Solutions, Semi, SIMTech Microfluidics Foundry, Skalene, SLAC National Accelerator Lab, Sony DADC, Stanford University, Stiplastics, TNO, University College London, University Twente, and many others.

Comments, suggestions and questions regarding this document can be addressed to:

Henne van Heeren enablingMNT –Netherlandshenne@enablingMNT.com 0031786300748

This work was supported by the Microfluidic Consortium and the MFManufacturing project, co-funded by grants from the UK, France and the Netherlands and the ENIAC / ECSEL Joint Undertaking.

Version 2.0, May 2016

DOI 10.13140/RG.2.1.1698.5206

# Mayor changes in the White Paper 2.0 versus 1.0

Besides correcting typos and adding additional clarifications, the following major changes have been made:

- 1) Par. 5.4 Sizes of fluidic ports: Table showing the relation between hole sizes, tissue punch size and needle nominal outer diameters.

- 2) Glass wafer thicknesses: transferred to whitepaper part 2

- 3) Edge connector: transferred to whitepaper part 2

- 4) Par 8: Exclusion zones around ports and exclusion zones for clamping

In part 2 of this white paper we will address: glass wafer thicknesses, edge connector and a route towards smaller chips.

# **Contents**

| V       | layor                              | changes in the White Paper 2.0 versus 1.0                                                                                | 2                              |   |

|---------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------|---|

| С       | onter                              | nts                                                                                                                      | 3                              |   |

| 1.      | . In                               | troduction                                                                                                               | 4                              |   |

| 2       | D                                  | efinitions around chips and connectors                                                                                   | 5                              |   |

| 3.      | . Pı                               | o forma standard chip sizes and interconnections                                                                         | 6                              |   |

| 4.      | St                                 | andard guidelines for axes and reference point                                                                           | 8                              |   |

|         | 4.1 XY axes for microfluidic chips |                                                                                                                          | XY axes for microfluidic chips | 8 |

|         | 4.2                                | Chip reference point                                                                                                     | 10                             |   |

| 5       | M                                  | licrofluidic port                                                                                                        | 10                             |   |

|         | 5.1                                | Port pitches                                                                                                             | 11                             |   |

|         | 5.2.                               | Nominal distance of the top or bottom fluidic port from the sides of the chip/substrate.                                 | 11                             |   |

|         | 5.3                                | Distance between two rows                                                                                                | 12                             |   |

|         | 5.4                                | Sizes of fluidic ports                                                                                                   | 13                             |   |

|         | 5.5                                | Fluidic port nomenclature                                                                                                | 13                             |   |

| 6<br>cł |                                    | ummary table of all interconnect guideline dimensions and tolerances regarding port pitche icknesses and port dimensions |                                |   |

| 7       |                                    | andard guide lines for chip formats                                                                                      |                                |   |

|         | 7.1                                | Outer chip dimensions in general                                                                                         | 16                             |   |

|         | 7.2                                | Microscope slide format standards                                                                                        | 16                             |   |

|         | 7.3                                | Credit card format                                                                                                       | 17                             |   |

|         | 7.4                                | Smaller chip format standards                                                                                            | 18                             |   |

| 8       | Ex                                 | cclusion zones                                                                                                           | 18                             |   |

|         | 8.1                                | Exclusion zone for the interfacing area (where the microfluidic ports are)                                               | 18                             |   |

|         | 8.2                                | Exclusion zone for clamping of the chip                                                                                  | 19                             |   |

| 9       | Se                                 | ensor / Actuator building blocks                                                                                         | 19                             |   |

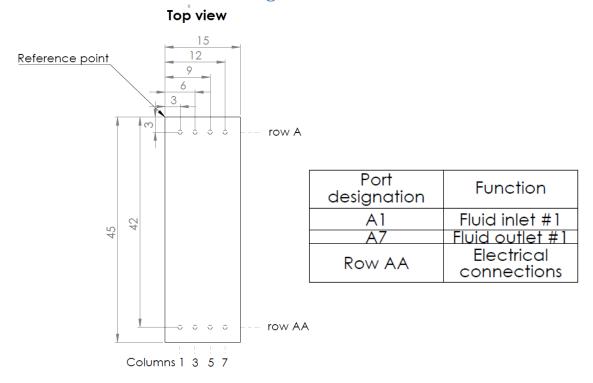

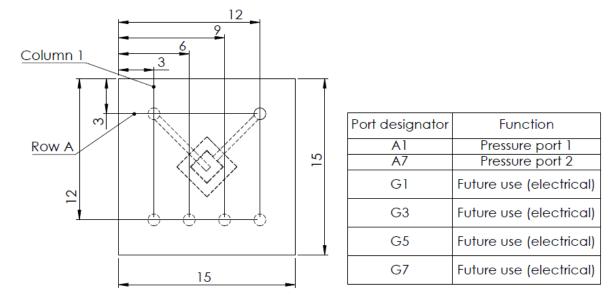

|         | 9.1.                               | 15x15 Microfluidic Building Blocks                                                                                       | 20                             |   |

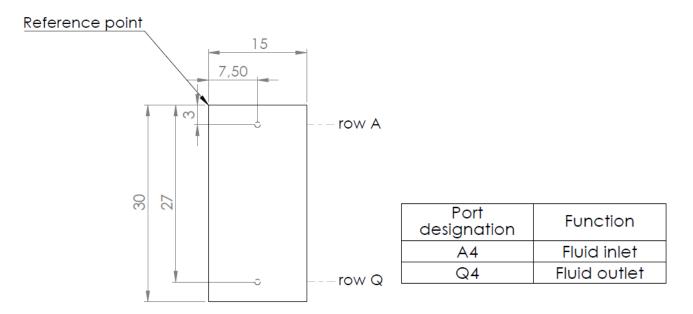

|         | 9.2.                               | 30x15 and 15x30 Microfluidic Building Blocks                                                                             | 21                             |   |

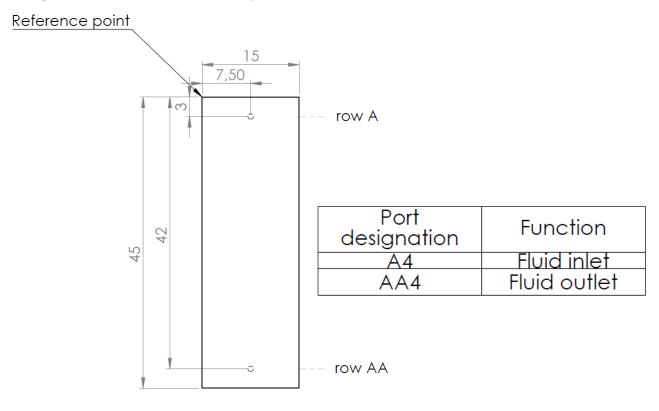

|         | 9.3.                               | 15x45 Microfluidic Building Blocks                                                                                       | 22                             |   |

|         | 9.4.                               | Sensor / Actuator Microfluidic Building Block with one inlet and one outlet                                              | 23                             |   |

| 1       | ) St                               | andard guidelines for operational conditions / application classes                                                       | 26                             |   |

| 1       | 1 Δι                               | nd Finally                                                                                                               | 28                             |   |

#### 1. Introduction

#### Context

The goal of this document is to facilitate the process of designing new microfluidic sensors, actuators, connectors etc. by providing guidelines for the seamless integration with other microfluidic components and systems. This will overcome the challenge that the process of moving from a research prototype device to a production device takes too long and is too expensive. This is such a barrier for startups in new technology that this phase is sometimes called the "Valley of Death". This is the case for a wide variety of materials and manufacturing processes. An important part of the challenge is that one often is designing without a clear guideline what the most appropriate method is to integrate it into a system or connect it to other devices. The flip side of the same argument is that potential users are often frustrated when components and systems presented to them are difficult, inappropriate or even impossible to interconnect with or integrate into their systems.

#### Objectives of this paper

This White Paper is an attempt to improve the situation. It is made available for free to developers and researchers around the world who are contemplating the creation of prototype devices containing microfluidics. Its purpose is to present developers a standard by which they will improve the chances of their device will be accepted by the marker / fits to other products.

#### Positioning of this paper

This paper is "application agnostic" – it is be relevant to people working in: Diagnostics, High Throughput Screening, Sample Preparation, Genomics, PCR, Circulating Tumour Cells, Regenerative Medicine, Flow Chemistry, Environmental, Food and Homeland Security Sensing... and beyond!

This paper is also "materials and production technology agnostic" — we recognise that microfluidic devices can be realised in PDMS, PMMA, COC, Polycarbonate, Glass, Silicon, Metal and Paper as different players specialize in / have a preference for different materials. Furthermore this paper is "manufacturing process agnostic" — recognising again that processes can by company specific. Our vision is that newcomers to the microfluidics market — and companies that want to expand their product portfolio — will look at the relevant guidelines and design according to them. The process to create the products based on these designs will not be described or discussed in this paper. The paper especially addresses topics related to the issue of the microfluidic connections to microfluidic chips or substrates and the integration of microfluidic chips or substrates in components and systems.

Using these design guidelines will be helpful for both user and supplier by ensuring plug and play interconnections.

It is intended that this will be a "living document" updated regularly and the authors are keen on feedback regarding how the document might be improved.

Note: This document does not guarantee IP freedom to operate! There is a complex landscape of patents around microfluidics devices so it is up to you to check whether you need a licence!

The chosen approach concerning the guidelines towards connection/interfacing is to provide the minimum guidelines needed for interoperability, leaving open which materials to be used, what

targeted applications and what connections types. We focused on keeping the guidelines simple, understandable by all and implementable by the product manufacturers as well as by the research labs. These guidelines are considered as a first essential step but certainly not an end point.

# 2 Definitions around chips and connectors

Connection the microfluidics on a chip or substrate to the outer world is less straightforward than many may think. Often this involves connecting manually channel by channel; a laborious activity and often leading to malfunction. This can be improved by using standardized (multiport) connectors. to enable these, agreements have to be made about the dimensions of the chips and the positions of the ports. As this industry lacks a common language even the discussion itself is complicated.

In order to clarify this, a few definitions will be given below. Also the area where our guidelines apply will be described.

We have considered two parts particularly important for interoperability: the chip and the connector.

The chip is a flat microfluidic device. Important are its format and the position of the fluidic inlets and outlets. Our guidelines will specify at least:

- The chip format

- The inlet /outlet port location

The connector is defined by two sides; the side connected to the chip and the other side that is left open and can be connected to a tube, an instrument, a fluidic circuit board, another chip, a sensor, etc...

Although one can easily represent a chip, it is much less true for the connector which is important to consider in a very broad way. Indeed in establishing these guidelines, we considered as connector not only typical connectors such as those sold by Dolomite, Micronit and others, but also the possibility to use other types of assembly methods such as adhesives (double face tape, glue..), O-rings with a clamping system or even the often used mini-Luers.

Not defining completely the connectors but only the side connected to the chip gives a huge freedom to operate, independently of the chip material or the chip to chip assembly method. However, defining only the geometry (port location, and foot print) is still a great achievement since it enables interoperability.

By defining only the chip geometry we avoid all the chip to chip, chip to fluidic circuit board, chip to outer world discussions, simplifying the problem to the chip and to the chip side of the connector. This simplicity enables a large number of users and manufacturers to consider using these guidelines.

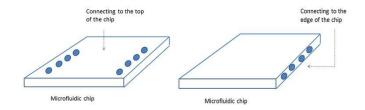

In order to better clarify chip topology we have agreed on the following terminologies represented in Figure 1:

- Top or Bottom connections (ToB connections)

- Edge connections

Figure 1: Schematics showing top side (left) and edge (right) connections.

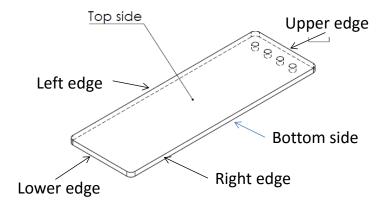

Figure 2 defines the nomenclature of the top and bottom chip sides as well as the left right upper and lower edges. It should be noted that the choice for defining the top and bottom sides is based on manufacturing practices. The person that is using such a chip under a microscope might have an opposite view!

Figure 2: Schematics showing top and bottom side and edge of the chips.

In some cases the using of the terms top and bottom side of the chip might cause confusion; for instance when such a chip is mounted on a microfluidic circuit board. In such cases, it is advised to use the terms interfacing side (where the ports are) and clamping area (the other side).

# 3. Pro forma standard chip sizes and interconnections

Although many different chip sizes are being used and can be used for microfluidics, for several reasons it might be advisable to adhere to certain chip sizes that are commonly used and supported by the supply chain.

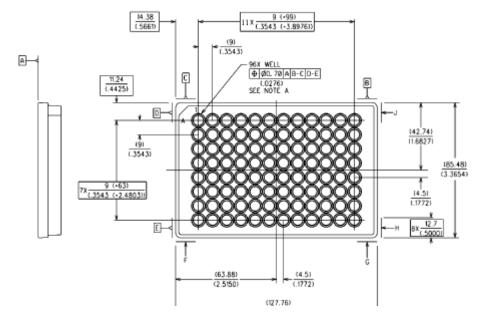

The analytical industry is using microtiter plates with standardized dimensions. (See: ANSI/SBS 4-2004). Based on this specification microfluidic chips are offered which have the same outer dimensions. When this chip size is used for microfluidics, the microfluidic connections are mostly miniLuers, placed on the borders of the chip with a pitch of 4.5 mm (or multiples of 4.5 mm) according to the positions of the outer wells of the standard layout. See Figure 3:

Figure 3: Layout of a microtiter plate (Courtesy ANSI/SBS 4-2004).

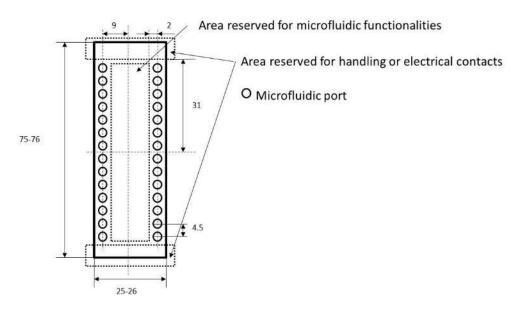

Another standard chip size often used is the microscope slide format. There is some variation in dimensions of those slides, but it seems that the industry is slowly heading towards 75 \* 25 mm size, although slightly larger slides (3 \* 1 inch) are still being sold. We strongly advice to use SI unit in microfluidics where possible.

There are two options to connect tubes to these slides: In the case of micromoulded chips, miniLuer interconnects at one or both of the long sides of the chip are the standard (see next Figure).

Figure 4: Layout of microscope slide commonly used in microfluidics with miniLuer interconnect positions

Although often used, the format above show several disadvantages, especially when one want to use multiport connectors, connectors with less dead volume or when one want to use smaller chips. Therefor the following paragraphs will present a more advanced set of standard configurations, containing optimized standard chip dimensions and positions of microfluidic ports.

# 4. Standard guidelines for axes and reference point

The objective of this part of the design guide is to provide a coherent system of reference axes used to describe positions on the chips. The convention is based on the chip manufacturing view point, not on the user who might take another view. We only address rectangular and square chips. The reason for this, lays in the objective of this paper, providing guidelines for microfluidic interconnections and integration. Circular disks are not discussed as they seldom need microfluidic connections and are generally used as standalone devices, i.e. seldom integrated.

#### 4.1 XY axes for microfluidic chips

General comment: the XY axis are chosen in such a way that for the description of a certain point only positive numbers need to be used.

#### Rectangular chips

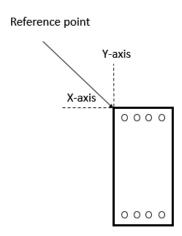

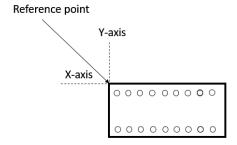

The naming of the chip defines the position of the XY axes. For instance a 15\*30 mm<sup>2</sup> chip has the X axes along the 15 mm side. The chip is then positioned with the X axis pointing from left to right. The Y axis is on the left of the viewer. The reference point is then on the top left of the chip<sup>1</sup> (see next Figure).

Figure 5: 15\*30 mm<sup>2</sup> chip with axes and reference point.

A 30\*15 mm<sup>2</sup> chip has the X axis along the 30 mm side. The Y axis is again on the left and the reference point on the top left corner. (See Figure 6.)

-

<sup>&</sup>lt;sup>1</sup> For details regarding the reference point see next section.

Figure 6: 30\*15 mm<sup>2</sup> chip with axes and reference point.

As a preference one should chose the naming (and with that the X axis) in such a way that (most of) the microfluidic connections are on the side of the X axis.

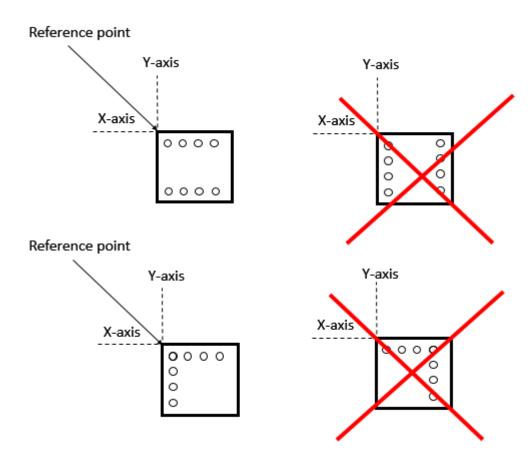

#### Square chips

For square chips, the positioning of the XY axis is more arbitrary, but again the preference is that (most of) the connections are near the X axis. If that would lead to two different options due to asymmetric placement of the microfluidic ports, one should choose the one with most of the ports near the reference point (See Figure 7).

Figure 7: Preferred positioning of XY axes and reference point for square chips.

#### 4.2 Chip reference point

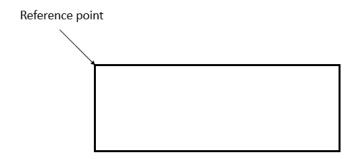

The reference point is the point where the two sides, named X and Y axes, cross.

Figure 8: Position of reference point determined by the two axes.

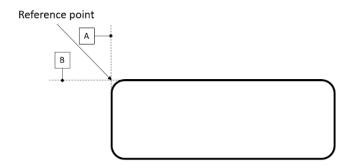

When a chip has rounded corners, as it is often the case with injection moulding, the crossing planes of the two sides of the chip, will be used as the reference point (Figure 9).

Figure 9: The position of the reference point at the crossing planes (A and B) of the two sides of the chip in presence of rounded corners.

If needed, in the case of symmetrical chips for example, the position of the reference point might be clearly marked by a marker in the vicinity of the reference point. If this is the case, a preferred option would be to locate identification markers on the left side of the chip in an index area. This is analogous to identifying or alignment markers in electronics (sometimes also called fiducials).

Several Identifying Markers can be used:

- Painted or printed markers are recommended when a simple orientation check of the chip is needed.

- A corner cut or notch can be considered if this is needed for the assembly process.

# 5 Microfluidic port

This section describes the available options for positioning the microfluidic ports on a chip, it size and the coding of the port position. This is particularly of relevance for those that want to design chips and ToB connectors that are truly interchangeable. These positioning rules are also used for the definition of the edge connector standard. But that is not all, these also provide guidelines for those that have an interest to connect microfluidic sensors and actuators to microfluidic circuit boards. Finally it had an influence on the early discussions about very small microfluidic chips and their connections.

#### 5.1 Port pitches

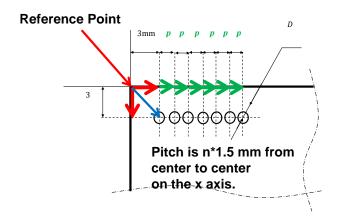

This section describes the available options for positioning the microfluidic ports on a chip. Of all geometrical dimensions, the port pitch, i.e. the distance between the centres of two ports is perhaps the most important parameter. It was decided that all the proposed layouts are to be based on a 1.5 mm grid<sup>2</sup>. Not all the holes are necessarily present on the chip or connector, but all the hole positions are fixed. This 1.5 mm grid enables several configurations. The hole positioning is always established from the reference point, in order to avoid cumulative drifts. A 1.5 mm pitch was chosen for the following reasons:

- Below 1.5 mm, according to manufacturers, it is at this moment not possible to have leakage free fluidic connections using the currently available multiport connection technologies.

- Microtiterplates are a well-established standard for tissue culture, cell-based assays, high throughput/content screening applications, etc. In addition, there are well established peripheral equipment suppliers for microtiterplate based liquid handling, processing and detection. The well positions in microtiterplates are compatible with the 1.5 mm grid<sup>3</sup>. Therefor 1.5 mm is also a good number to accommodate:

- MiniLuers (widely used in microfluidics ) have a 4.5 mm pitch.

- Microtiter plate well spacing for reservoirs filling by a multi pipette for example.

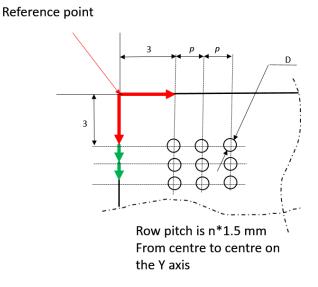

Figure 10: Top view of ToB connections showing the position of the row of hole at a distance of centre to centre of 1.5 mm from each other on the X axis.

There is a preference for a 3.0 mm port pitch (n=2). In the microfluidic field, 3 mm spacing is considered as state of the art for spacing between ports. In the near future chips and connectors with 1.5 mm pitches will likely become available.

# 5.2. Nominal distance of the top or bottom fluidic port from the sides of the chip/substrate

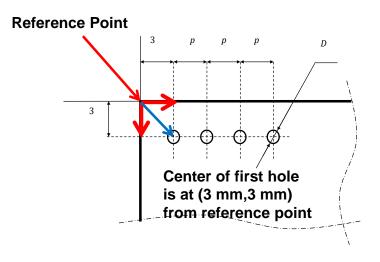

Due to restrictions in manufacturing technology it was decided that the centre of a top or bottom port should always be at a distance of at least 3 mm from all sides.

<sup>&</sup>lt;sup>2</sup> In the future this nominal value may be extended to a smaller one (0.75 mm instead of 1.5 mm). One of the reasons will be to open a route towards miniaturization.

$<sup>^3</sup>$  1536 well plate has a pitch of 2.25 mm between well, which is incompatible with the 1.5 mm grid, but is compatible with the envisioned future standard grid of 0.75 mm.

. This 3 mm distance was adopted after discussion with injection moulding manufacturers, assuring that such a distance from the edge ensured a robustness when using injection technologies.

Following this restriction, the position of the first allowed hole/fluidic port position near the reference point is now defined as being at position (3 mm, 3 mm). (see Figure 11).

Figure 11: Top view of ToB connections showing the position of the first hole at a distance of 3 mm from each side of the top left corner of the chip.

#### 5.3 Distance between two rows

Distance between two rows is a multiple of 1.5 mm (p\*1.5 mm) from centre to centre on the y axis (Figure 12). Not all the rows are necessarily present on the chip or connector, but row positions are fixed. This 1.5 mm grid enables several configurations. The row positioning is always established from the reference point, in order to avoid cumulative drifts. The same reasoning was applied to the Y axis as the one used for the X axis. There is a preference for a 3.0 mm row pitch (p=2).

Figure 12: Top view of ToB connections showing the position of the rows at a distance of centre to centre of 1.5 mm from each other on the y axis.

#### 5.4 Sizes of fluidic ports

Controlling the diameter for fluidic ports are important for leak free connections, reduction of dead volume and flow resistance. As diameter sizes are very much dependent on the fabrication technology it is very difficult to standardize them in total. However, minimum and maximum recommended diameters (d) of the port on the surface of the chip are:

1.5 mm pitch: 0.4 < d < 0.7 mm</li>

3.0 mm pitch: 0.4 < d < 2.0 mm</li>

4.5 mm pitch: 0.4 < d < 3.5 mm</li>

Indeed, depending on the needed pressure and flow rate, diameters may need to vary in order to control pressure loss and dead volumes. However microfluidic chip and connector manufacturers considered that a distance of 1 mm between holes is required to have a good microfluidic connection. This therefore provided the upper limit of the range. An exception was made for the 1.5 mm pitch for which 0.7 mm maximum was required in order to provide a sufficient port diameter.

For PDMS chips, university researchers widely use tissue punch or syringe needle to fabricate fluidic access hole. In addition, for PMMA/PDMS chip, many university researchers glue syringe needles on the chip inlet/outlet as fluidic access interface with tubing. Both tissue punch or syringe needle have their own size standard<sup>4</sup>. The defined hole sizes are compatible with the tissue punch sizes, as shown in the following table:

Table 1: Relation between hole sizes, tissue punch size and needle nominal outer diameters

| Pitch (mm) | Hole size (mm) | Tissue punch size (mm) | Needle Nominal outer diameter (gauges) |

|------------|----------------|------------------------|----------------------------------------|

| 1.5        | 0.4 < d < 0.7  | 0.5                    | 27-17 gauges                           |

| 3          | 0.4 < d < 2.0  | 0.5, 1                 | 27-12 gauges                           |

| 4.5        | 0.4 < d < 3.5  | 0.5, 1, 1.5, 2         | 27-8 gauges                            |

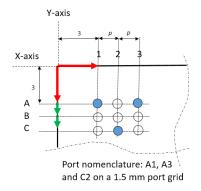

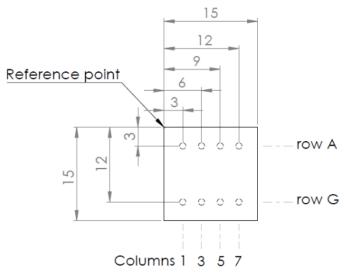

#### 5.5 Fluidic port nomenclature

Fluidic port nomenclature was proposed to simplify fluidic chips design, guidelines and instructions. We have adopted the same convention as the microtiter plate format used to identify wells: numbers for columns and letters for rows.

The first possible grid position in the left corner, closest to the reference point, would be A1, the next one on the X axis with a distance of 1.5 mm will be A2. Numbers increase from left to right and letters from upper to lower edge (Figure 13).

The fluidic port grid follows the standard pitch definition of 1.5 mm and can unambiguously identify port locations on a chip. The chess board type notation for fluidic ports helps to prevent mistakes between fluidic ports and electrical interconnect in a chip design where both types of interconnects are used. The generic grid is 1.5 mm pitch but the 3 mm pitch corresponds to the preferred configuration.

\_

<sup>&</sup>lt;sup>4</sup> Hypodermic needles are available in a wide variety of outer diameters described by gauge numbers. Smaller gauge numbers indicate larger outer diameters. Inner diameter depends on both gauge and wall thickness.

Figure 13: Top view of ToB connections showing fluidic port, nomenclature based on a 1.5 mm grid.

As a final remark it should be noted, that this universal system for port positioning still needs in each case clarification about the character of each port (incoming, outgoing fluids etc.) or even existence of the port: not all positions might be used for microfluidic interconnections.

# 6 Summary table of all interconnect guideline dimensions and tolerances regarding port pitches, chip thicknesses and port dimensions

The relevant guidelines for ToB connectors are summarized in the table below:

Table 2: Key parameters for top interconnection standardization and tolerances.

| Parameters  Parameters                                                                       | Nominal value | Minimal value | Maximal value | Tolerance             |

|----------------------------------------------------------------------------------------------|---------------|---------------|---------------|-----------------------|

| Reference point : Left chip corner                                                           |               |               |               | 0 mm                  |

| Distance of the first hole from the reference point (3 mm, 3mm) (corner edge to hole centre) | (3 mm, 3 mm)  |               |               | +/- 0.15 mm           |

| Minimal distance of any hole from any side of the chip                                       |               | 3 mm          |               |                       |

| Distance between holes or port pitch (centre to centre)                                      | n*1.5 mm      | 1.5 mm        |               | +/- 0.15 mm           |

| Rows are parallel to the chip's x axis at a distance from ref. point of n*1.5                | n*1.5 mm      | 1.5 mm        |               | +/- 0.15 mm           |

| Port diameter for 1.5 mm grid                                                                |               | 0.4 mm        | 0,7 mm        |                       |

| Port diameter for 3 mm grid                                                                  |               | 0.4 mm        | 2.0 mm        |                       |

| Port diameter for 4.5 mm grid                                                                |               | 0.4 mm        | 3.5 mm        |                       |

| Tight tolerance of outer chip dimension (desired) <sup>5</sup>                               |               |               |               | + 0.05 / - 0.15<br>mm |

| Lower tolerance of outer chip dimension (when tight tolerance not achievable)                |               |               |               | +/- 0.3 mm            |

-

<sup>&</sup>lt;sup>5</sup> Needed for some connector or chip holder systems

# 7 Standard guide lines for chip formats

Due to the diversity in the market, standardisation of chip formats is a difficult topic, but after analysing the situation and discussions with major players, we were able to propose here some guidelines that fit as best as possible to the demand. We added to those standard formats the position of the microfluidic ports according to the standards we developed before (see section 4).

## 7.1 Outer chip<sup>6</sup> dimensions in general

The outer chip dimensions are important for standardization. Chip formats are described in the next section. However it is important to fix the desired tolerances, while allowing for less accurate manufacturing processes. We have defined an asymmetrical tolerance for limiting oversize chips which will not fit in holders and connectors:

- Maximum / desired oversize is (+ 0.05 mm)

- Maximum undersize is (- 0.15 mm)

- Preferred undersize is (- 0.05 mm)

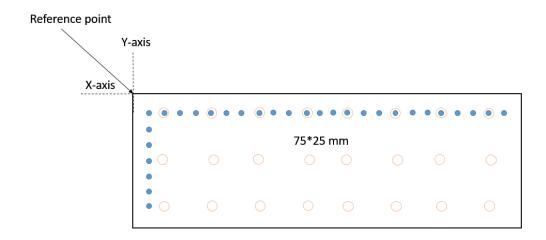

### 7.2 Microscope slide format standards

The official microscope slide standard<sup>7</sup> allows all sizes in length between 76 and 74 and in width 26 and 24 mm. This will not work for affordable and reliable connectors. The two most commonly used dimensions are 75.6 x 25.4 and 75 x 25. We have chosen the slide format that fits best to the grid of 1.5 mm, which is therefore the  $25.0 \times 75.0 \text{ mm}$  slide format.

In order to have symmetrical connectors, we have modified the first hole location for this format: the first hole position will be at 3.5 mm<sup>8</sup> from the long edge and 3.0 mm from the short edge.

#### Microscope slide X1:

Figure 14: 75\*25 mm microscope slide with ports having 3 mm pitches (blue); the microtiter plate well positions in a 9 mm grid are shown for reference (in orange)

<sup>&</sup>lt;sup>6</sup> All chip sizes mentioned in this report refer to chipsizes after dicing.

<sup>&</sup>lt;sup>7</sup> Standard Microscope slide: ISO (International Organization for Standardization) 8037-1:1986.

<sup>&</sup>lt;sup>8</sup> This is unfortunate deviation from the general rule, caused by the size of the slide.

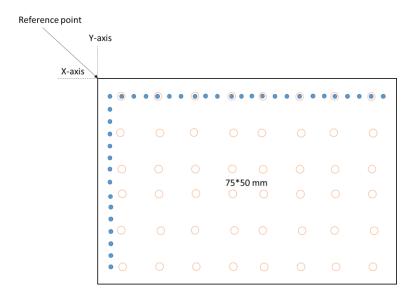

#### Microscope slide X2:

Some users have a double microscope slide format, in this case  $50.0 \times 75.0 \text{ mm}$  is the standard chip format. The first hole position will be  $4 \text{ mm}^9$  from the long edge and 3.0 mm from the short edge.

Figure 15: 75\*50 mm microscope slide with ports having 3 mm pitches (blue); the microtiter plate well positions in a 9 mm grid are shown for reference (in orange)

#### 7.3 Credit card format

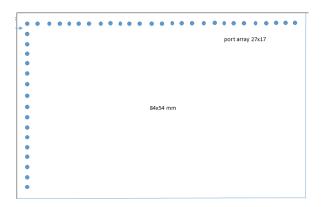

The credit card format with its well-established manufacturing production lines is often used in the industry and may be important for providers of microfluidic devices. For this reason, we have included this format which is  $85.60 \times 53.9810$  mm. To make it better compatible with the 3 mm pitch preference, we propose the following "credit card" format: 84 mm x 54 mm (see Figure 16).

Figure 16: Top view of credit card chip format showing in blue the standard fluidic ports for one row and one column.

17

<sup>&</sup>lt;sup>9</sup> This is unfortunate deviation from the general rule, caused by the size of the slide.

### 7.4 Smaller chip format standards

Although, as shown above, there are standard chip formats for the larger chip sizes, no such standard exists yet for smaller chips. That is an unfortunately situation; there is much interest to go to smaller chip sizes. For the moment we propose to use footprints that are a multiple of 15 mm in the X and Y directions. This size has been chosen because an investigation by one of the MFManufacturing partners showed that this is a format used by several companies. It is also identical to the standard coverslides: 15\*15; 30\*30 and 60\*60.

Furthermore, it is compatible with the 1.5 mm pitch and can accommodate a wide range of applications. That is not the end of the discussion; already there are voices that vote for chip sizes smaller than 15\*15 mm.

#### 8 Exclusion zones

To be able to achieve a leak free connection and a mechanical strong fixation, a sealing area on the interfacing side (where the ports are) and an area reserved for clamping the chips are needed.

# 8.1 Exclusion zone for the interfacing area (where the microfluidic ports are).

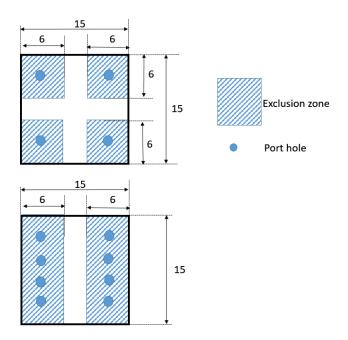

In order to achieve leak free microfluidic connection between a chip and a connector it is advised to define a 6\*6 mm<sup>2</sup> square with centre port in the middle of that square. Prohibited in this zone are: structures that create obstructions on the surface and structures that create holes, dents etc. in the surface (except the portholes itself of course). (see next figure)

Figure 17: exclusion zones around portholes; example 15\*15 mm chip

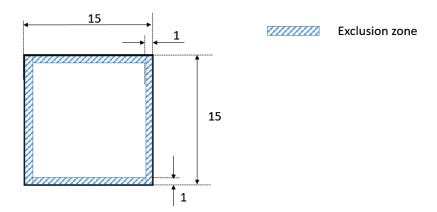

### 8.2 Exclusion zone for clamping of the chip

If a sensor or actuator chip is attached to a circuit board with clamping designers should take care that a strip of 1 mm wide at the opposite side of the chip is reserved for clamping purposes. This area should be free of obstructing structures. (see next figure)

Figure 18: clamping zone for 15\*15 mm<sup>2</sup> chip

Although a clamping zone of 1 mm wide is sufficient for chips with sizes of 15\*15 mm<sup>2</sup> or smaller, for larger chips wider clamping zone might be needed. Larger clamping zones may also be needed for applications where pressures up to 30 bars are being used.

# 9 Sensor / Actuator building blocks

In many cases it is easier to position a sensor direct onto another component or device without using tubes for interconnections. For instance placing them on a microfluidic circuit board analogue to placing a transistor on an electronic circuit board. This part of the guidelines defines the geometries required to ensure plug and play interconnections and interoperability in such situations. Mechanical fixture can be done for instance by gluing or clamping<sup>11</sup>. We advise here generic design rules for the templates of the most common building blocks (15x15 and 15x30).

We identify three types of connections: fluidic connections, pneumatic and electrical connections.

\_

<sup>&</sup>lt;sup>11</sup> The specification of the area on top of the chip needed for clamping will be specified later.

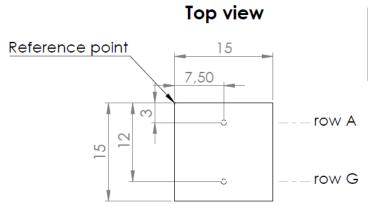

# 9.1.15x15 Microfluidic Building Blocks

# Top view

| Port designator | Function               |

|-----------------|------------------------|

| A1              | Fluid inlet #1         |

| A7              | Fluid outlet #1        |

| Row G           | Electrical connections |

Figure 19: Top view 15x15 Microfluidic Building Block with multiple ports.

| Port<br>designation | Function     |

|---------------------|--------------|

| A4                  | Fluid inlet  |

| G4                  | Fluid outlet |

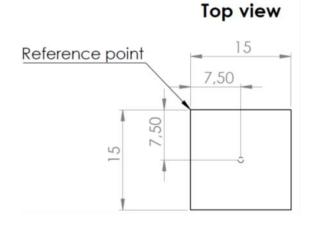

Figure 20: Top view of 15x15 Microfluidic Building Block with ports centred on short edges.

Figure 21: Top view of 15x15 Microfluidic Building Block with a single centred port in D4 position.

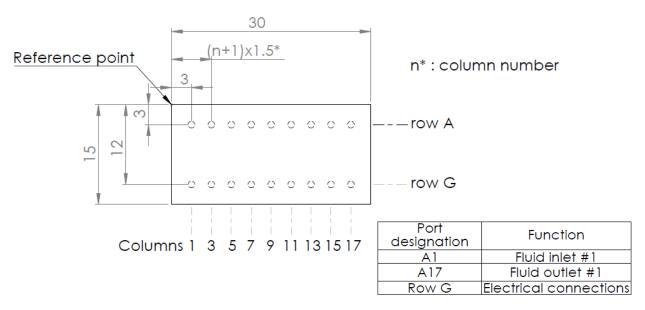

# 9.2. 30x15 and 15x30 Microfluidic Building Blocks

# Top view

Figure 22: Top view of a 30x15 mm building block with ports on the long side.

| Port designation | Function               |

|------------------|------------------------|

| A1               | Fluid inlet #1         |

| A7               | Fluid outlet #1        |

| Row Q            | Electrical connections |

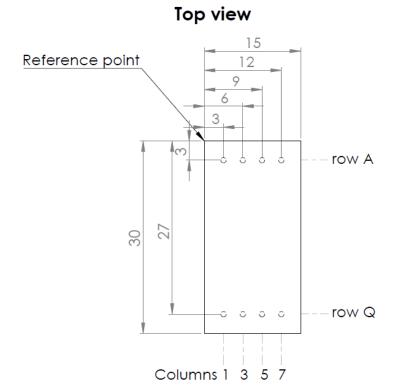

Figure 23: Top view of a 15\*30 mm building block with ports on the short side.

# Top view

Figure 24: Top view of a 15\*30 mm building block with centred ports.

# 9.3. 15x45 Microfluidic Building Blocks

Figure 25: 15x45 Microfluidic Building Block with multiple ports on the short side.

Figure 26: 15x45 Microfluidic Building Block with centred ports.

# 9.4. Sensor / Actuator Microfluidic Building Block with one inlet and one outlet

Figure 27: Sensor block layout with fluidic and electrical interconnections (1)

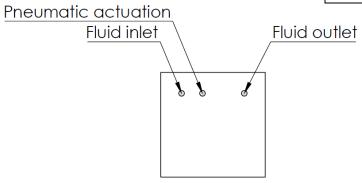

Pneumatic Valve Building Block

| Port designation | Function            |

|------------------|---------------------|

| A1               | Fluid inlet         |

| A3               | Pneumatic actuation |

| A7               | Fluid outlet        |

Figure 28: Sensor block layout with fluidic and pneumatic interconnections (2)

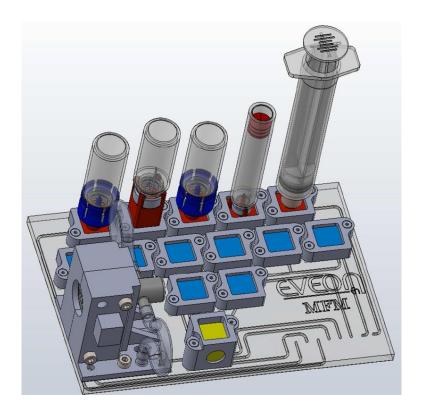

# 9.5. Example of the use of standardized sensor / actuator interfaces

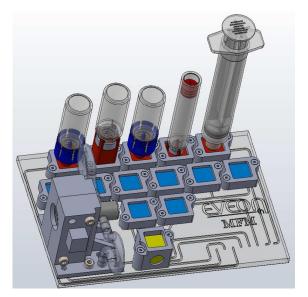

The next Figure shows an example where companies have made use of the standardized sensor / actuator layout (dimensions and port pitches). The components on the microfluidic circuit board (they are from several suppliers), all adhere to the proposed standards discussed above. The valves and sensors (light blue), the interface block (red) and the actuator (yellow), all are 15 \*15 mm² blocks. The microfluidic ports connecting those parts to the microfluidic circuit board (not visible) are all on the grid positions described before.

Figure 29: Example of the use of sensor / actuator standard to create a complete functional tool (courtesy EVEON)

# 10 Standard guidelines for operational conditions / application classes

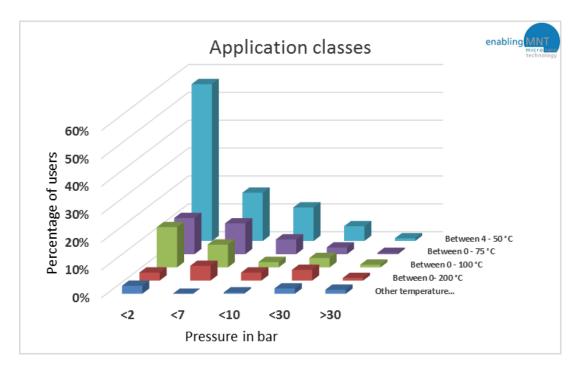

This part is still under discussion and is provided here as an example of how we will proceed rather than a final version of operational condition limits. We came to this point by an iterative process using surveys to check our initial assumptions. Temperature and pressure were chosen as key elements for the operating conditions while they are closely linked to the applications and have important consequences in terms of manufacturing chips or connectors. Depending on the conditions temperature or pressure, material choice will be impacted as well as the design.

The first survey provided a coarse overview of the field. The proposed temperature and pressure ranges for the second survey were chosen based on the following considerations:

- The temperature range 4 50 °C was chosen while this range is used by many suppliers of off the shelve pumps.

- The temperature range 4 100 °C is chosen to cover also applications using polymerase chain reaction (PCR)

- On advice of some suppliers, who felt that the difference between 50 and 100 °C was too much, 75 °C was chosen as a upper limit too.

- 2 And 7 bar are maximum pressures that are quite commonly used by suppliers to specify their products. The other limits are based on the outcome of the first survey. The second and third survey provided more information about the distribution of the user over the classes. (see Figure 30)

Figure 30: Distribution of the users of microfluidics over the classes (from a survey).

Based on this outcome we created a first proposal for operating classes:

Table 3: Proposal for application classes.

| Classes  | Maximum        | Maximum          | Minimum          |

|----------|----------------|------------------|------------------|

|          | pressure (bar) | Temperature (°C) | temperature (°C) |

| PT 2/50  | 2              | 50               | 4                |

| PT 2/75  | 2              | 75               | 4                |

| PT 2/100 | 2              | 100              | 4                |

| PT 7/50  | 7              | 50               | 4                |

| PT 7/100 | 7              | 100              | 4                |

| PT 30/50 | 30             | 50               | 4                |

Table 3 presents only a starting point in relation to classification. Undoubtedly a more comprehensive classification scheme is envisaged, once other distinctive features like for instance flow and media used will be taken into account. It is therefore likely that other classes and sub-classes will be introduced into the scheme of things, which will be explored in follow up surveys. For example, we will explore if this classification system can be extended to cover different media used, thus taking into account if the device is designed for chemicals or biologicals. In addition, the classification system will need to take into account special devices, such as those that operate at higher pressures/temperatures than those listed in the table. For example, the classification system will need to be extended to take into account special cases such as HPLC-Chip technology, where pressures are significantly higher than those listed.

## 11 And Finally

As said, this White Paper is not a final document; it is just a reflection of the first discussions about microfluidic standards. Several new topics will be addressed in part 2 of this white paper, addressing chip thicknesses, edge connectors and further miniaturization. Experienced engineers will find many other details to specify. For instance those interested in shorter times to market and higher reliability will stress the need for industry wide accepted validation tests etc. etc.. Therefor we (and hopefully you too) will regard this as a living document. We are interested in your feedback and involvement to improve it!

We are grateful to the ENIAC /ECSEL project MFManufacturing and the Microfluidic Consortium that have supported this work. And thanks to many, many engineers and researchers who actively participated in the many discussions leading to this document.

| To be continued |

|-----------------|

| <br>            |