# Standards for the microfluidic industry

Henne van Heeren, enablingMNT

Status February 2017

#### Mission

- Facilitating the uptake of microfluidics by simplifying the integration of microfluidic components and systems and pushing towards lower costs, shorter time to market and reusability in multiple applications.

- More specifically by:

- Defining industry wide supported guidelines and standards that will enable reliable microfluidic interconnections and affordable integration,

- supported by standardized application specific verification test to guarantee fitness for use.

### History 2010-2015

- 2010: started standard discussion in the Microfluidic Consortium

- 2012: article in Lab on Chip journal published

- 2013: white paper manufacturing guidelines

- 2014: start MFManufacturing project

- 2014: first survey on microfluidic connections

- 2015: Second survey: reliability of microfluidics based devices and components

- 2015: Third survey: microfluidic flow control

- 2015 first white paper: chip formats, microfluidic interconnections, microfluidic building blocks and operational conditions / application classes

### History 2016

- First white paper updated

- Second white paper: chip thicknesses, edge connectors and further miniaturization of chips and connectors

- Fourth survey: interaction of sensors and microfluidics

- ISO document accepted: Guidelines for pitch spacing dimensions and initial device classification

- New Work Item proposed to ISO: Microfluidic Standardisation

- Fifth survey: testing of microfluidic devices

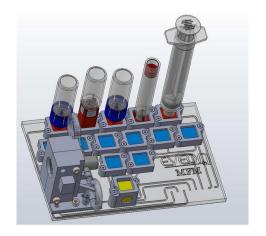

- About 10 new products in development based on these standards

17/02/2017

### Standard discussions up till now

- Decision to make them material, technology and application agnostic.

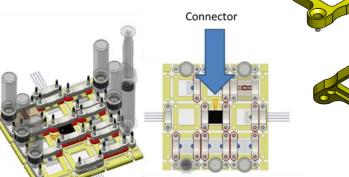

- Microfluidic interconnections (top- and edge connectors)

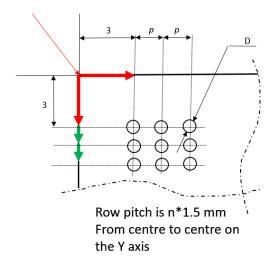

- Position, size and coding of microfluidic ports

- Sensor and actuator building blocks

- Dimensions, position, size and coding of microfluidic and other ports, clamping mechanisms

- Operational conditions / application classes

- Chip size / interconnections roadmap

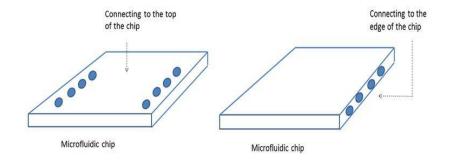

#### Microfluidic interconnections

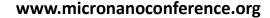

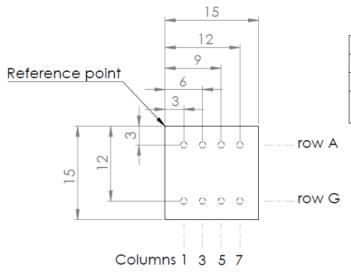

#### Reference point

Layout of ports on chips (topconnectors)

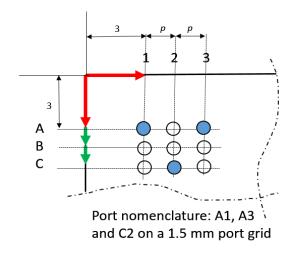

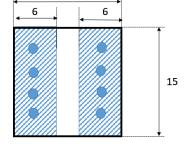

Layout of ports on the edge of a chip (edge connectors)

Microfluidic Standardisation, status February 2017

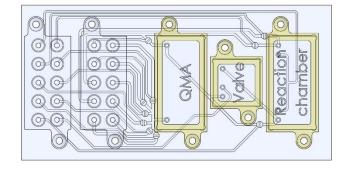

### Sensor and actuator building blocks

Top view

| Port designator | Function               |

|-----------------|------------------------|

| A1              | Fluid inlet #1         |

| A7              | Fluid outlet #1        |

| Row G           | Electrical connections |

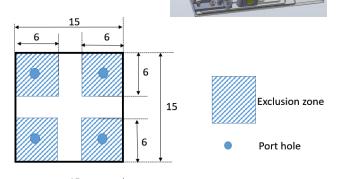

exclusion zones around portholes; example

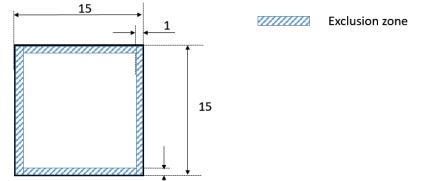

clamping zone for 15\*15 mm chip 15\*15 mm chip Microfluidic Standardisation, status February

17/02/2017

2017

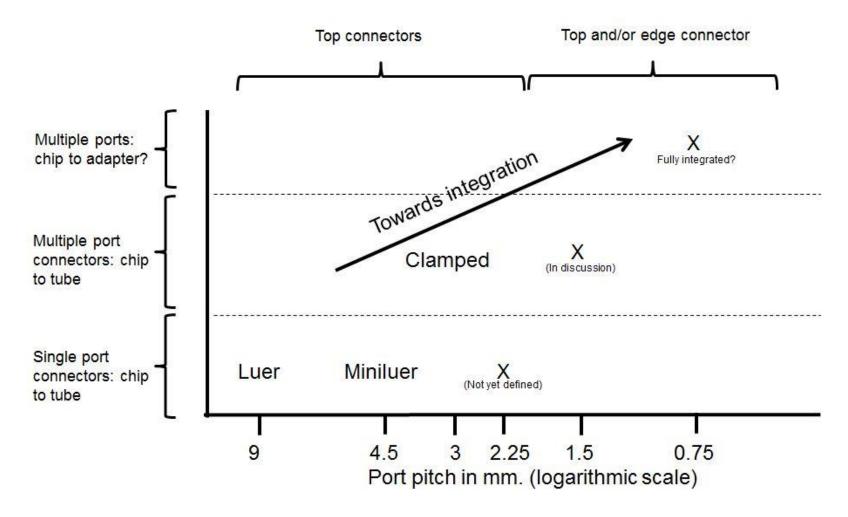

### Roadmap to further integration

### Top connector roadmap

|                     | 1 <sup>st</sup> Gene                        | ration                                                     | 2 <sup>nd</sup> Gen                  | eration                         | 3 <sup>nd</sup> Generation       |   |  |

|---------------------|---------------------------------------------|------------------------------------------------------------|--------------------------------------|---------------------------------|----------------------------------|---|--|

| Applications        | Lab<br>instrume                             | ntation                                                    | Sensi                                | ing                             | ?                                |   |  |

| Products            | Pumps,<br>(sensors                          |                                                            | Also<br>biose                        | ensors                          | ?                                |   |  |

| Chip sizes          | 15*15 a                                     | nd larger                                                  | 7.5*7.5                              | (or 7.5*6?)                     | ?                                |   |  |

| Grid                | 1.5                                         |                                                            | 1.5                                  | 5                               | 0.75?                            |   |  |

| Port pitch          | 3                                           |                                                            | 1.5                                  | 5                               | ?                                |   |  |

| Distance<br>to edge | 3                                           |                                                            | 3 (                                  | (or 1.5?)                       | ?                                |   |  |

| Technologies        | Tube based:<br>top or<br>bottom<br>clamping | Surface<br>mounted:<br>clamping<br>(and under<br>pressure) | Tube based:<br>also edge<br>clamping | Surface<br>mounted:<br>also ??? | Only<br>integrated?<br>Imposers? | Ş |  |

### Edge connector roadmap

|                     | 1 <sup>st</sup> Generation | 2 <sup>nd</sup> Generation | 3 <sup>nd</sup> Generation |

|---------------------|----------------------------|----------------------------|----------------------------|

| Applications        |                            | Ctrl) ▼                    |                            |

| Products            |                            |                            |                            |

| Chip<br>thicknesses | 2/2 ; 2/1                  | 2/0.7; 1/0.7;<br>0.7/0.7   | x/0.4?                     |

| Grid                | 1.5                        | 1.5                        | ?                          |

| Port pitch          | 3                          | 3                          | ?                          |

| Distance<br>to edge | 3                          | 3                          | ?                          |

| Technologies        | Tube to chip               | Tube to chip via a seal    | ?                          |

|                     |                            |                            |                            |

## Roadmap port pitch and distance to the edge

| Distance     | Port  | Technology status                                                    |

|--------------|-------|----------------------------------------------------------------------|

| to side      | pitch |                                                                      |

| 3            | 3     | State of the art, technology proven                                  |

| 3            | 1.5   | State of the art, technology proven                                  |

| 1.5          | 1.5   | Candidate for next step in roadmap,                                  |

|              |       | technology feasible                                                  |

| 3            | 0.75  | Likely not a standard                                                |

| 1.5          | 0.75  | Likely not a standard                                                |

| 0.75         | 0.75  | Candidate for future step in roadmap,                                |

| 47 100 10047 |       | technology challenging Microfluidic Standardisation, status February |

17/02/2017

# Roadmap chip / package size (in relation to port pitches and distance to the edge, dimensions in mm)

|          |       | Maximum number of ports on <u>one</u> side |     |   |     |   |     |   |          |   |   |    |    |            |

|----------|-------|--------------------------------------------|-----|---|-----|---|-----|---|----------|---|---|----|----|------------|

|          |       | 1                                          | 2   | 3 | 4   | 1 | 2   | 3 | 4        | 1 | 2 | 3  | 4  | # of ports |

| Distance | Port  |                                            |     |   |     |   |     |   |          |   |   |    |    |            |

| to side  | pitch |                                            |     |   |     |   |     |   |          |   |   |    |    |            |

| 3        | 3     |                                            |     |   |     |   |     |   |          | 6 | 9 | 12 | 15 | Chip /     |

| 3        | 1.5   |                                            |     |   |     | 6 | 7.5 | 9 | 10.5     |   |   |    |    | package    |

| 1.5      | 1.5   | 3                                          | 4.5 | 6 | 7.5 |   |     |   |          |   |   |    |    | size       |

|          |       |                                            |     |   |     |   |     |   | February |   |   |    |    |            |

17/02/2017 Microfluidic Standardisation, status February

## Microfluidic surveys (MFM supported)

- Microfluidic interconnections (August 2014)

- Microfluidic reliability (February 2015)

- Microfluidic flow control (September/October 2015)

- (Bio)sensors (May/June 2016)

- Microfluidic test guidelines (November/December 2016)

- TBD spring 2017

### White papers

- Design for Microfluidic Device Manufacture Guidelines (Microfluidic Consortium initiative, 2014)

- Design Guideline for Microfluidic Device and Component Interfaces (MFM initiative, December 2015, update expected soon)

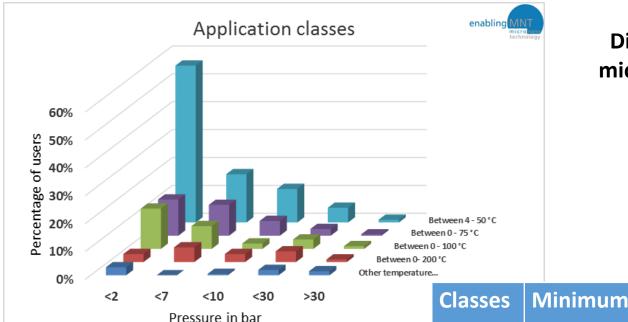

### Operational conditions / application classes

Distribution of the users of microfluidics over the classes (survey results).

Proposal for application classes.

Microfluidic Star

| Classes         | William        | Maximani    | Maximani     |  |  |

|-----------------|----------------|-------------|--------------|--|--|

|                 | temperature    | Temperature | pressure     |  |  |

|                 | (°C)           | (°C)        | (bar)        |  |  |

| A               | 4              | 50          | 2            |  |  |

| В               | 0              | 75          | 2            |  |  |

| С               | 0              | 100         | 2            |  |  |

| D               | 4              | 50          | 7            |  |  |

| Е               | 0              | 100         | 7            |  |  |

| ndardisation, s | tatus February | 50          | <b>30</b> 15 |  |  |

### White papers

- Manufacturing:

- Design for Microfluidic Device Manufacture Guidelines (Microfluidic Consortium initiative, 2014)

- Interconnection

- Design Guideline for Microfluidic Device and Component Interfaces Part 1 and Part 2 (MFM)

- In preparation: Integration of microfluidics

### Design Guideline for Microfluidic Device and Component Interfaces

#### • Editors:

Henne van Heeren (enablingMNT), Tim Atkins (Blacktrace/Dolomite), Nicolas Verplanck and Christine Peponnet (CEA-LETI), Peter Hewkin (CfBI), Marko Blom and Wilfred Beusink (Micronit), Jan-Eite Bullema (TNO), Stefan Dekker (University of Twente).

- With contributions / suggestions and support from persons from the following organisations:

- APIX, Axxicon, Bronkhorst, CEA-Leti, CfBI, CMC Microsystems, Corsolution, Cytocentrics, Diagnostics Biosensors, DIBA, Dolomite, enablingMNT, EV Group, EVEON, Fluigent, Fraunhofer IOF, IHP, IMTag, IMTEK, Invenios, IPHT, IVAM, LioniX, Memsmart, Microfluidic ChipShop, Microfluidic Consortium, Micronit, MinacNed, NIST, Philips, PhoeniX, Qmicro, SCHOTT Technical Glass Solutions, Semi, SIMTech Microfluidics Foundry, Skalene, SLAC National Accelerator Lab, Sony DADC, Stanford University, Stiplastics, TNO, University College London, University Twente, and many others.

### enabling MNT

### New products based on these standards

Courtesy: Tronics, TNO, PMB, Philips, Micronit, MESA+, Medimetrics, Fluigent, Eveon, Dolomite, CEA-Leti, Axxicon, APIX

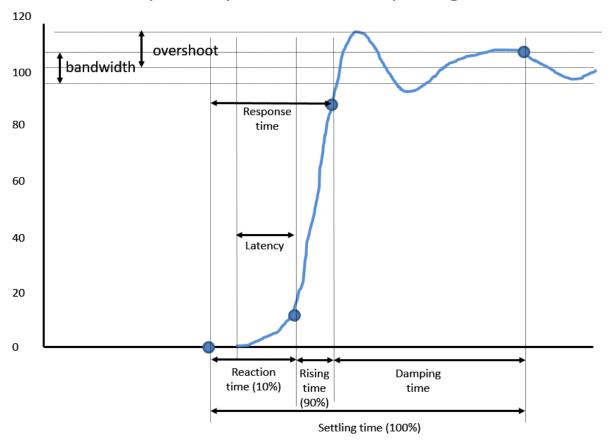

### Flow control terminology

Flow rate stability and responds time to a step change in flowrate

### Plans 2017 / 2018

- Workshop NIST on standardisation 1,2 June.

- Start-up ISO workinggroup / subcommittee, addressing electrical connections and operational classes.

- Pursue discussion about (reliability) testing.

- Sixth survey, no topic yet selected.

- Third white paper: integration of microfluidics

- Start discussion about flow control standards.

- Start discussion about a roadmap to further integration / miniaturization.

### NIST Workshop on Standards for Microfluidics 2017

On June 1 & 2, 2017, NIST will host the first workshop on standards for microfluidics, which will be held at the NIST Gaithersburg Campus in Maryland (USA). In the last two decades this field has evolved from the concept of Micro Total Analysis Systems, where systems with integrated pretreatment and analysis of chemicals were envisioned, to what is known today as Lab on a Chip. This field has shown great potential for the development of technologies that can, and to some extent, are making the difference in areas such as in vitro diagnostics, point of care testing, organ on a chip and many more. Microfluidics plays an essential role in these systems and determining the standards needed in this area is critical to enable new markets and products, and advance research and development. Our goal is to bring together stakeholders from industry, academia and government to discuss and define what are the needs in the field for the development of standards. This will be a unique and exciting opportunity for stakeholders from all over the world to join in the discussion of future developments towards the standardization in the microfluidics arena.

### Where science and business discuss microfluidics, photonics & nanoinstrumentation

The International MicroNanoConference Amsterdam **12 & 13 December 2017** provides an unique platform for the world of Microsystems and Nanotechnology bringing together the **entire value chain**. It distinguishes itself by focussing on the **business opportunities** as well as the **practical applications** of the scientific research that is conducted by a growing number of companies and institutions.

The 2017 edition is held again at the impressive **Beurs van Berlage** in the heart of vibrant Amsterdam.

Meet the international MicroNano community and participate with a presentation, table top booth, as a sponsor or visitor!